El panorama de la computación ha experimentado un avance crucial gracias al reciente desarrollo de IBM en chips de señal mixta in-memory.

Computación Analógica en Memoria: El Futuro de la IA

En el afán de perfeccionar la velocidad y eficiencia energética de los dispositivos computacionales, surge la computación analógica in-memory (AIMC). Esta tecnología busca unificar cálculos y almacenamiento de datos en un solo componente, optimizando procesos y maximizando rendimiento. La integración de operaciones y comunicaciones digitales se vuelve esencial para lograr estos objetivos.

Los avances en inteligencia artificial y algoritmos de aprendizaje profundo han exacerbado la demanda de dispositivos que puedan manejar grandes cargas de almacenamiento y computación. Estos requisitos han propulsado investigaciones en el campo de AIMC, siendo una solución prometedora.

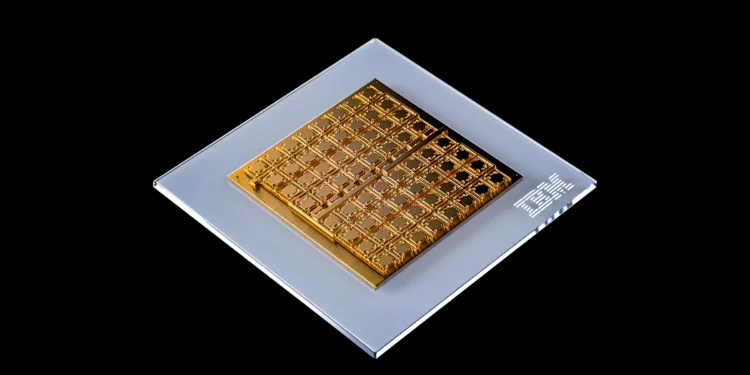

El nuevo chip de 64 núcleos de IBM, surgido de la investigación en IBM Research Europe, se basa en dispositivos de memoria de cambio de fase, prometiendo resultados notables en términos de velocidad y eficiencia energética sin comprometer la precisión de los algoritmos de aprendizaje profundo.

Dispositivos de Memoria de Cambio de Fase en la Vanguardia

Los dispositivos de memoria de cambio de fase (PCM) han sido un foco central en la investigación de IBM durante más de 7 años. Estos dispositivos han demostrado ser eficaces para implementar funciones neuronales y tienen potencial en aplicaciones que van desde la computación científica hasta la inferencia de redes neuronales profundas.

Manuel Le Gallo, uno de los autores del estudio, destaca que han demostrado que el uso de dispositivos PCM como elementos de cálculo resulta ventajoso en diversas aplicaciones. La visión es avanzar hacia la creación de un chip acelerador de inferencia de IA analógica de extremo a extremo.

La combinación de núcleos basados en PCM con procesadores de computación digital ha permitido la creación de un chip que consta de 64 núcleos analógicos basados en PCM, optimizando las capacidades de cálculo y almacenamiento.

Especificaciones del Chip: Un Acercamiento Técnico

El diseño del chip incorpora una matriz de barras cruzadas de 256 por 256 células de unidades sinápticas en cada núcleo. Esta estructura optimiza el procesamiento y la eficiencia del almacenamiento de datos.

Adicionalmente, se han integrado convertidores analógico-digitales compactos en cada núcleo para facilitar la transición entre operaciones analógicas y digitales. Estos núcleos también se benefician de unidades de procesamiento digital que implementan funciones de activación neuronal de unidad lineal rectificada (reLU) y operaciones de escalado.

En el núcleo central del chip, se ha integrado una unidad de procesamiento digital global especializada en operaciones de red de memoria a largo-corto plazo (LSTM), esencial para la optimización de tareas de aprendizaje profundo.

Red de comunicación digital: el corazón del chip

Una característica sobresaliente del nuevo chip es la incorporación de núcleos de memoria interconectados mediante una innovadora red de comunicación digital. Esta configuración permite realizar cálculos asociados a las capas individuales de una red neuronal en el mismo chip. El resultado es una drástica reducción en los tiempos de cálculo y el consumo energético.

El equipo dirigido por Le Gallo emprendió una evaluación exhaustiva de este chip, sometiéndolo a algoritmos de aprendizaje profundo. El conjunto de datos CIFAR-10 sirvió como campo de pruebas para las redes neuronales profundas, alcanzando una precisión en reconocimiento de imágenes del 92,81 %.

“Esta precisión es inédita para chips con tecnología similar”, señala Le Gallo. Además, destacó la sinergia entre la computación analógica in-memory con unidades de procesamiento digital y una robusta comunicación digital.

Comparativa: El avance sobre chips anteriores

El rendimiento por área, registrado para multiplicaciones matriciales de entrada-salida de 8 bits de 400 GOPS/mm2, es más de 15 veces superior al de anteriores chips multinúcleo basados en memoria resistiva. Sin embargo, la eficiencia energética es comparable, lo que evidencia una optimización superior en el nuevo diseño.

El trabajo reciente de IBM Research Europe representa un progreso significativo en la creación de chips AIMC diseñados para las demandas actuales de algoritmos de aprendizaje profundo.

Se espera que futuras actualizaciones del diseño presenten mejoras aún más significativas en rendimiento y eficiencia.

El futuro: Aceleradores de inferencia y arquitectura avanzada

Con base en el aprendizaje obtenido del chip actual y un chip previo de 34 baldosas presentado en 2021, el equipo ha diseñado una arquitectura avanzada. Esta nueva arquitectura de acelerador de inferencia de IA analógica se presentó recientemente en la revista IEEE Transactions on VLSI systems.

La visión propuesta combina múltiples mosaicos de computación analógica in-memory con núcleos de computación digital especializados, interconectados mediante una malla 2D paralela. Además, el entrenamiento basado en hardware desarrollado en años recientes promete precisión equivalente al software en diversos modelos neuronales.

Este avance, aunado a la precisión y eficiencia energética demostrada, establece un nuevo estándar para la industria y abre un amplio espectro de posibilidades en aplicaciones prácticas.

Citas y referencias clave

Más información sobre este tema puede encontrarse en el estudio “A 64-core mixed-signal in-memory compute chip based on phase-change memory for deep neural network inference”, publicado en Nature Electronics (2023) bajo la autoría de Manuel Le Gallo et al. La DOI asociada es: 10.1038/s41928-023-01010-1.